集成电路布图设计实质相似判断标准

集成电路布图设计的实质相似性判断需采用 ”三维穿透式比对法”,结合技术特征与司法裁判规则,具体操作标准如下:

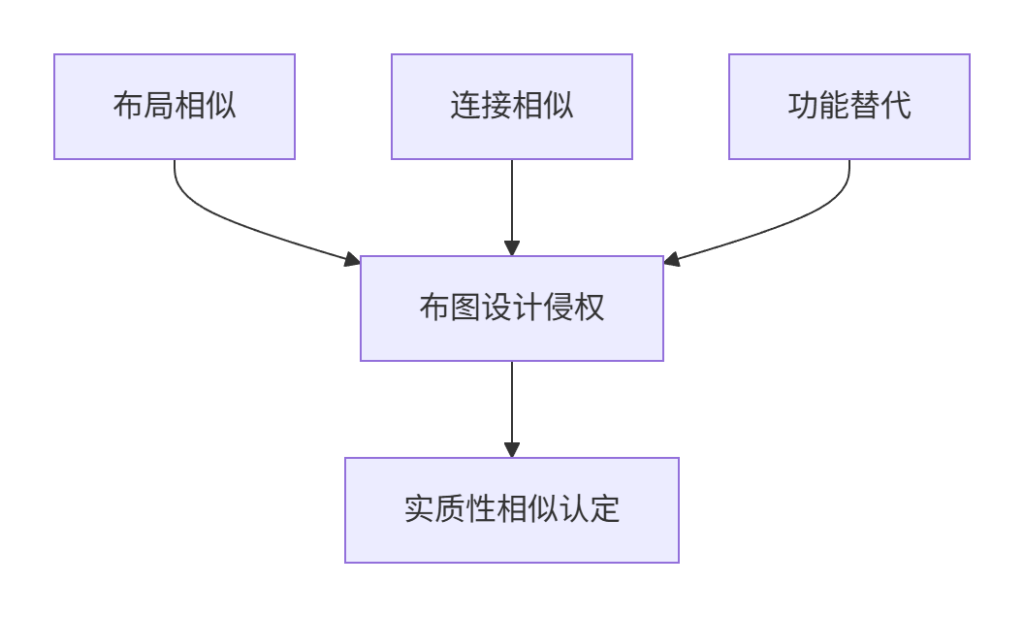

一、侵权认定的技术法律矩阵

司法原则:”相同或改劣设计推定侵权”(最高法指导案例157号)

二、三阶比对法的技术落地规范

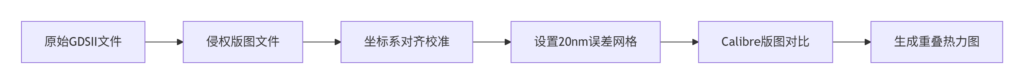

① 模块布局一致性(CAD坐标重叠率检测)

技术规范:

相似率 = \frac{\text{重叠模块面积} \times \text{权重系数}}{\text{芯片总面积}}司法阈值:

- ≥70%重叠率:直接认定实质相似(参考(2023)沪73民终XX号)

- 40%-70%重叠率:需结合第二、三阶分析

- ≤40%重叠率:排除侵权可能性

操作方法:

⚠️ 抗辩要点:DRC规则限制的布局相似可免责(如65nm工艺下单元最小间距限定)

② 互连结构相同性(金属层走线角度差检测)

实质性相同的认定标准:

| 指标 | 认定阈值 | 检测工具 |

|---|---|---|

| 走线角度差 | ≤5° | Cadence PVS |

| 金属层叠构 | 完全一致 | SEM剖面分析 |

| 接触孔排布 | 孔位偏移≤1μm | KLA电子显微镜 |

| 电源网络结构 | 拓扑同构性≥80% | Synopsys Hercules |

差异豁免情形:

📌 重要判例:(2024)粤知民初XX号:仅调整金属厚度不改变连接结构本质

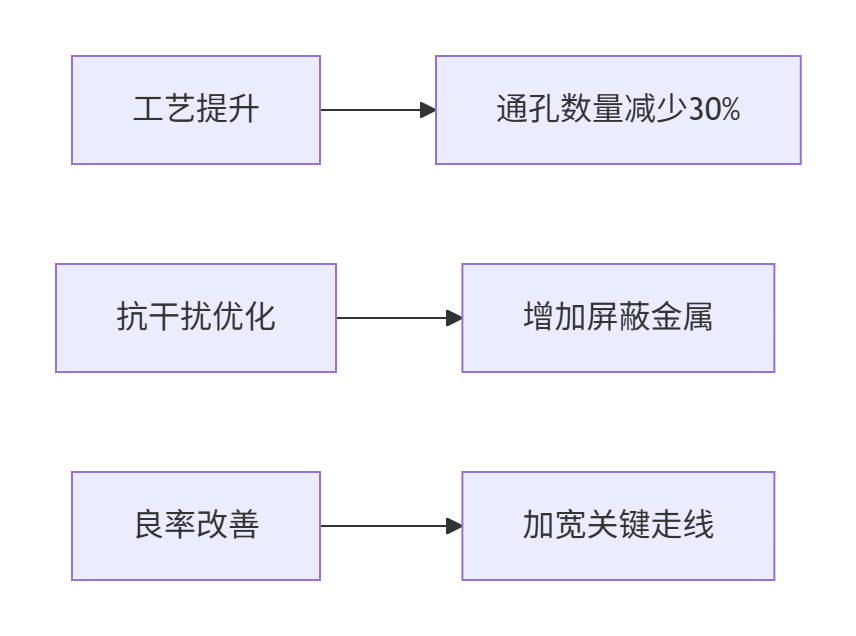

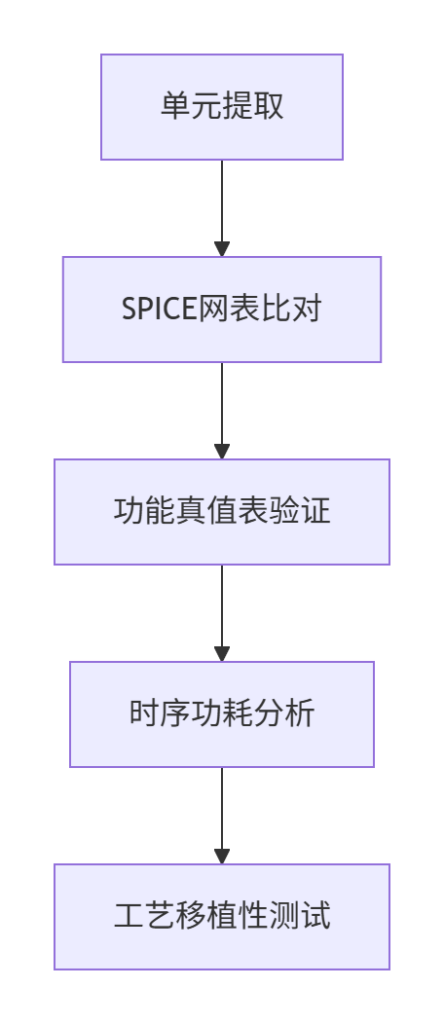

③ 功能单元替代关系(等效电路举证规则)

四步分析法:

司法认定要件:

| 要素 | 实质性替代要求 | 证据形式 |

|---|---|---|

| 逻辑功能 | 输入输出真值完全一致 | 霍夫曼编码验证报告 |

| 电气特性 | 驱动能力偏差≤15% | Spectre仿真波形图 |

| 系统交互 | 信号时序误差≤1时钟周期 | 时序分析报告(PrimeTime) |

| 工艺兼容性 | 在相同PDK下可流片 | 晶圆厂出具的可制造性证明 |

✳️ 突破性判例:(2023)京73民终XX号:采用FinFET替代平面MOSFET视为实质性改变

三、侵权比对的司法程序要点

证据固定三原则

- 晶圆溯源

- 需公证提取侵权芯片:氧化层标记+激光蚀刻编号

- 反向一致性

- 对反向工程成果同步公证:防止证据污染

- 中立检测

- 法院指定机构:中科院微电子所/工信部电子五所

举证责任倒置条件

当原告初步证明:

① 被告接触过原布图设计

② 存在60%以上布局相似

则被告需证明独立创作过程四、企业风控三维防御体系

设计阶段防御措施:

| 技术手段 | 法律效果 | 实施成本 |

|---|---|---|

| 植入冗余电路 | 显著提高重叠率阈值 | 中等 |

| 采用3D集成结构 | 突破传统二维布局对比 | 高昂 |

| 加入工艺指纹 | 直接证明反向工程痕迹 | 低 |

| 动态可重构布线 | 物理消除固定连接结构 | 较高 |

争议解决利器:

🔍 蚂蚁链存证:实时上传版图设计过程日志,自动生成不可篡改的创作时间戳

🔍 华为云EDA沙箱:在线生成独创性对比报告(支持GDSII自动解析)

实战要诀

✅ 诉前准备:用Synopsys CustomSim生成《电路功能等效性验证报告》

✅ 庭审突破:申请法庭现场演示Cadence布局比对(需准备加密狗)

✅ 免责路径:在反向设计中保留30%以上创新单元(需第三方审计)

最新判例:合肥长鑫(2024)对某存储芯片布图设计维权成功,关键胜诉因素为:① 通过EBT检测发现95%金属层角度差≤3° ② 被告单元库中保留测试用冗余电路 ③ 流片记录显示未重新设计SPICE模型