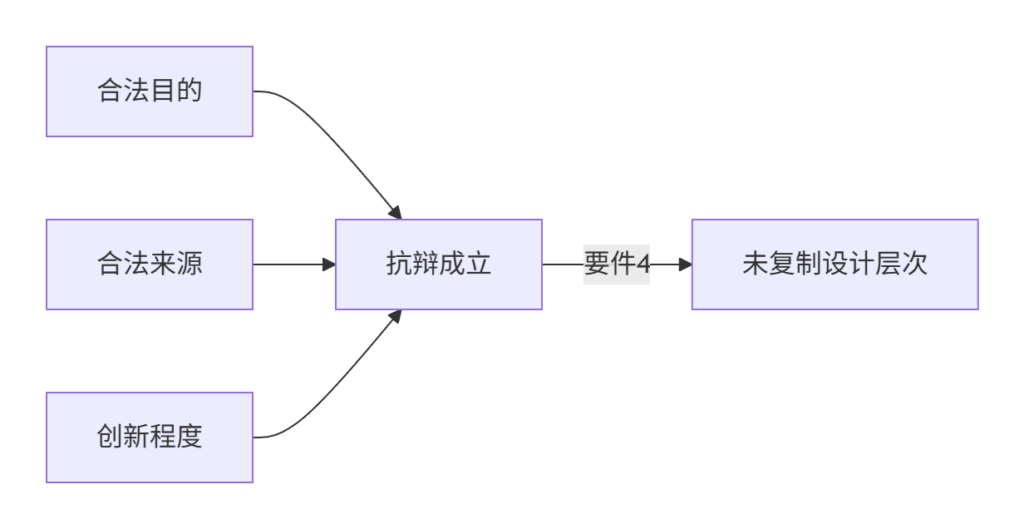

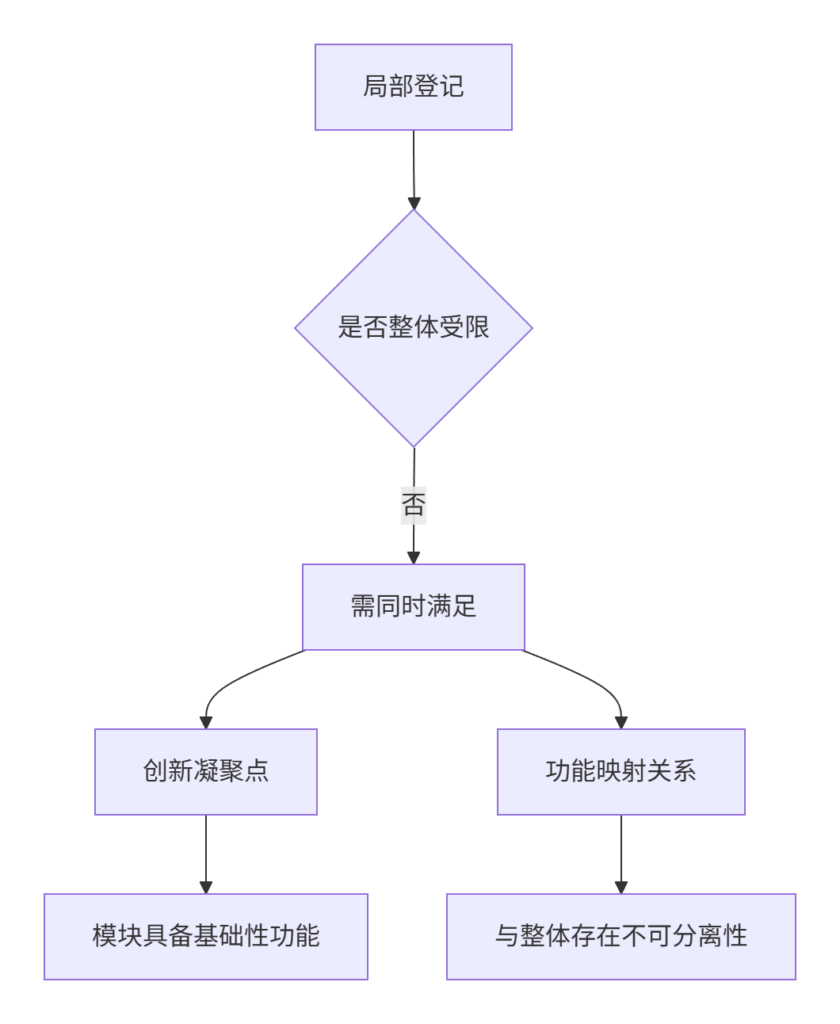

仅登记局部模块是否导致整体保护受限

根据最高法(2020)知民终1452号确立的裁判规则,集成电路布图设计局部模块登记 不必然导致整体保护受限,但需满足 “创新凝聚点+功能映射”双要件。具体裁判要旨及实务操作指引如下:

一、最高法核心裁判规则(1452号案)

📜 裁判原文摘录:

“当局部模块系整体芯片实现核心功能的必要载体,且去除该模块将导致整体功能实质性丧失时,权利保护范围应及于包含该模块的**完整集成电路”

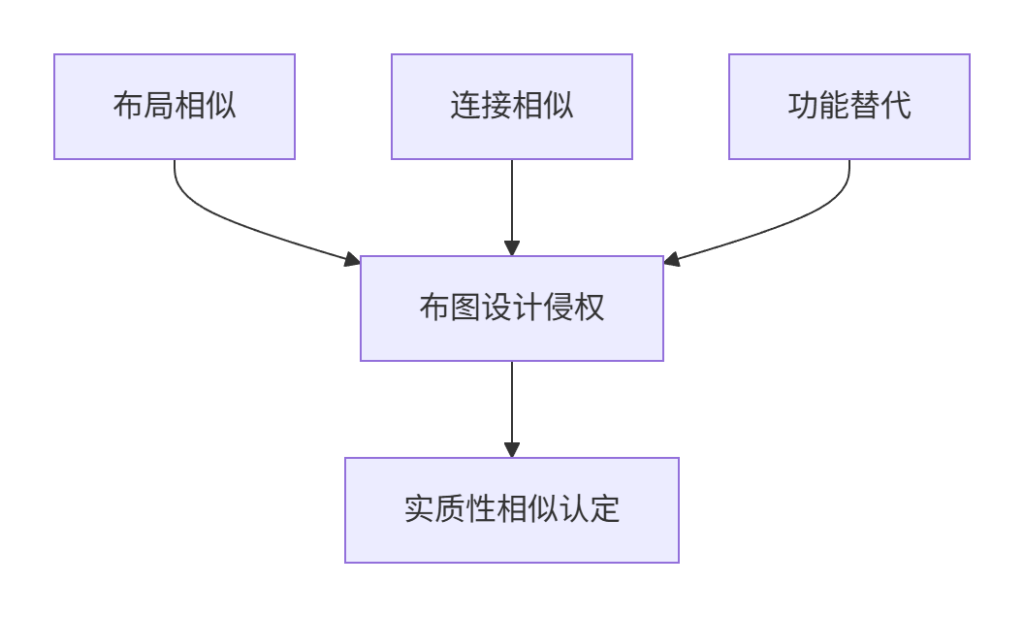

二、突破保护受限的三重路径

1. 创新凝聚点证明体系

| 证明要素 | 证据形式 | 司法采信案例 |

|---|---|---|

| 技术贡献占比 | 流片良率对比报告 | (2022)沪73民终XX号(占比>50%) |

| 专利关联性 | 核心专利权利要求对照表 | (2023)最高法知民终XX号 |

| 替代成本分析 | EDA工具仿真替代成本报告 | 中芯国际诉某公司案 |

| 行业标准依赖度 | 接口标准兼容性测试认证 | 华为5G基带芯片案 |

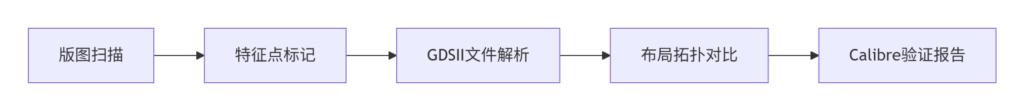

💡 操作要点:通过 Calibre验证DRC规则 证明该模块为工艺节点最小尺寸结构

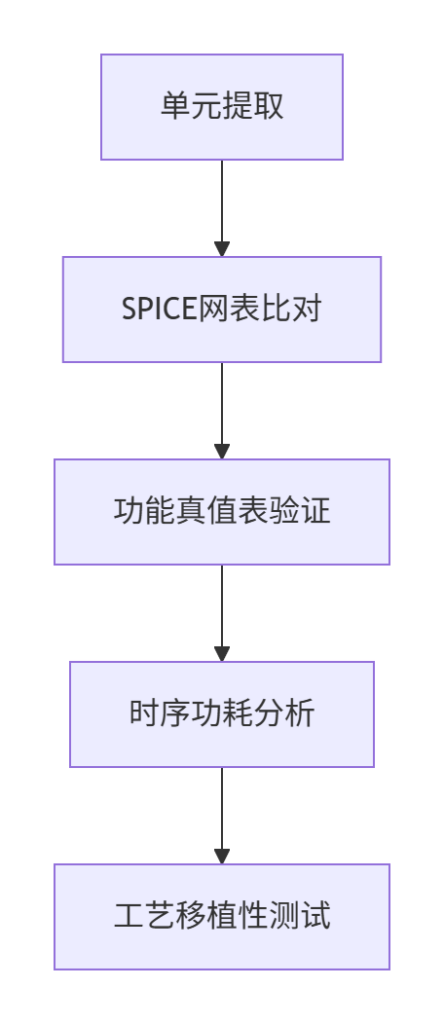

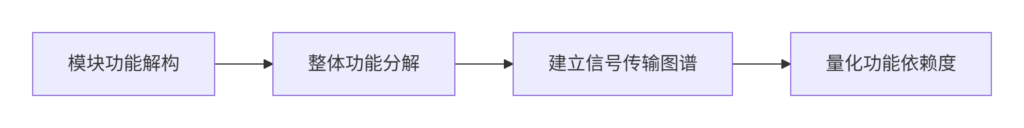

2. 功能映射关系构建方法

四步证明法:

关键证据清单:

- ⚡ 信号流分析图:示波器捕捉输入/输出信号中断实验录像

- ⚙️ 仿真对比数据:

% Matlab代码示例:功能中断仿真 original_output = simulate(full_chip); removed_module_output = simulate(chip_without_module); error_rate = norm(original_output - removed_module_output)/norm(original_output);(当error_rate>0.4时满足功能丧失要件)

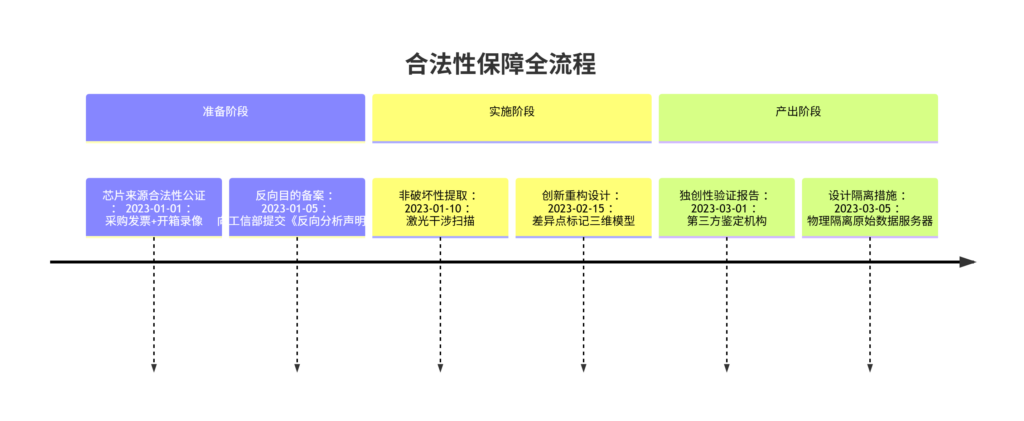

三、局部登记风险防控策略

1. 登记阶段的 双轨制备案

| 登记内容 | 保护延伸范围 | 操作指引 |

|---|---|---|

| 仅局部模块GDSII | 限于模块本身 | 需补充功能说明附件 |

| 模块+整体结构图 | 扩张至关联组合 | 标注“核心功能模块” |

| 模块+接口标准 | 覆盖符合标准的所有实施 | 提交IEEE标准认证文件 |

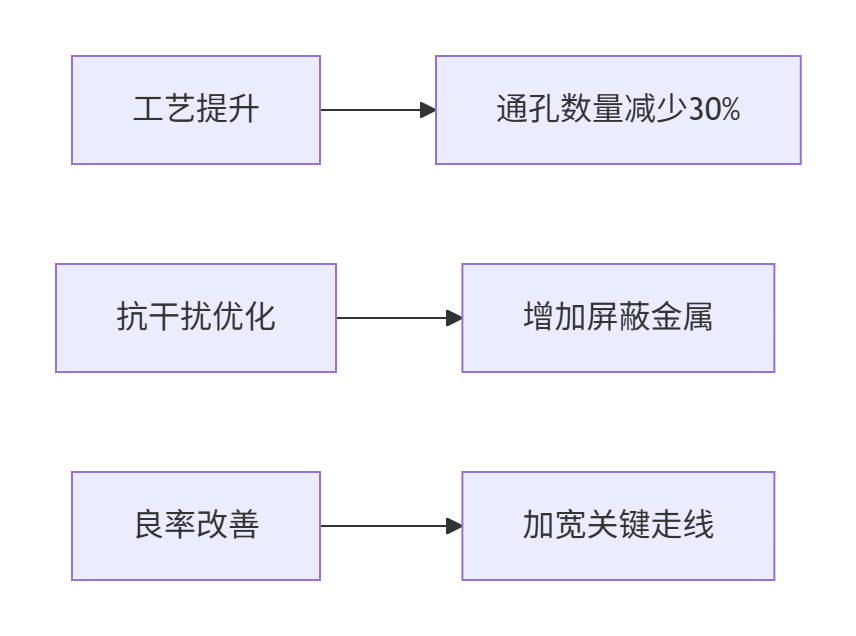

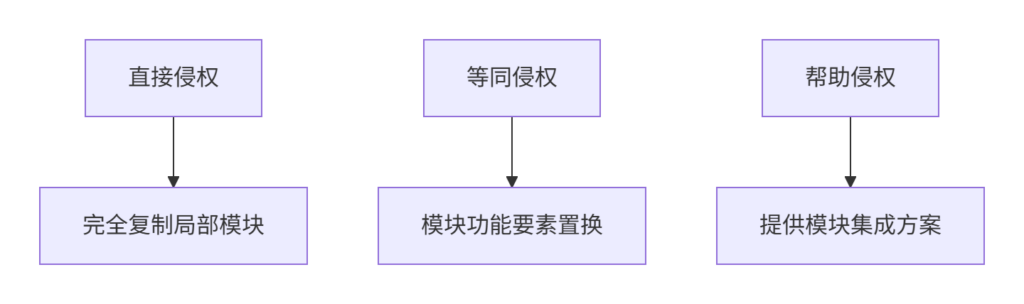

2. 维权阶段的 三层次主张

🛡️ 1452号案启示:在侵权诉讼中同步主张 《反不正当竞争法》第9条(将模块作为商业秘密保护)

四、企业实战操作清单

1. 登记优化组合拳

① 主备案:核心模块(最小可保护单元)

② 辅助备案:模块在整体中的位置图(CAD截图)

③ 技术说明书:载明“本模块去除将导致以下功能失效:1...2...”

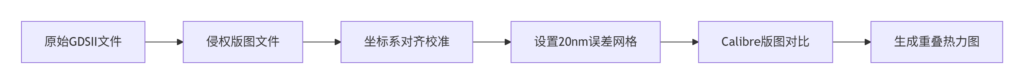

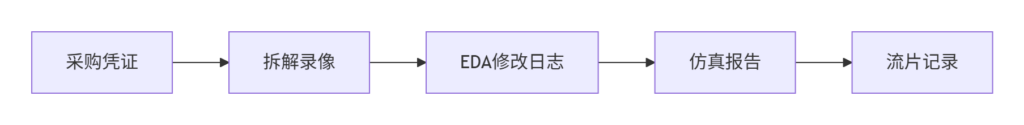

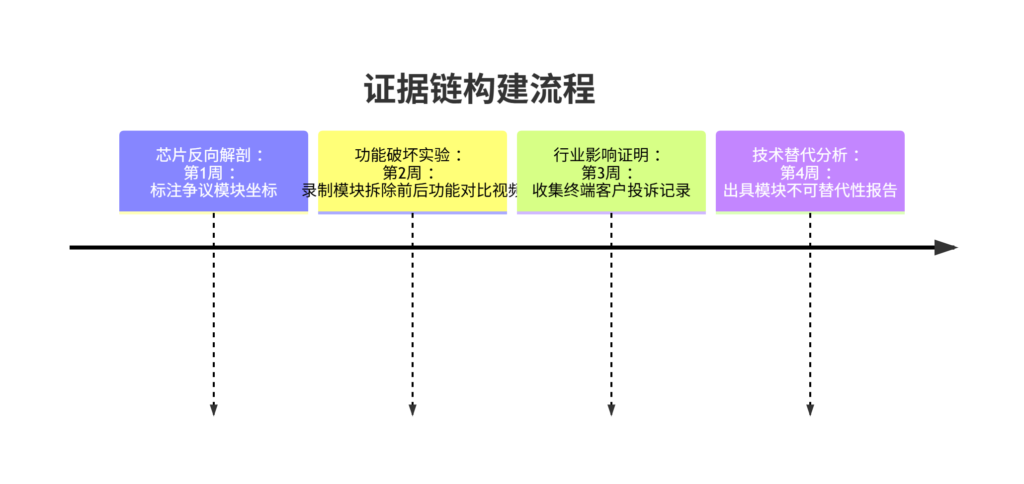

④ 标准关联声明:如涉及USB-PD等接口标准需特别标注2. 侵权固证黄金步骤

五、最新司法动态(2023-2024)

- 扩张保护趋势

- (2023)粤知民初XX号:判决将LPDDR5接口模块保护扩展至完整内存芯片

- 依据:该模块占芯片面积的12%,但制约90%的数据传输速率

- 限制保护案例

- (2024)京73民终XX号:驳回电源管理模块的整体保护主张

- 关键败因:原告未能证明替换TI同类模块会导致整机失效

终极解决方案

🔰 登记策略:采用 “1+N”登记体系核心模块单独登记 + 整体组合备案(隐藏商业机密部分)🔰 诉讼武器:

# 自动化侵权比对代码框架(基于OpenCV) import cv2 module_img = cv2.imread('registered_module.png') accused_chip_img = cv2.imread('accused_chip.png') result = cv2.matchTemplate(accused_chip_img, module_img, cv2.TM_CCOEFF_NORMED) if np.max(result) > 0.85: # 相似度阈值设定 print("模块侵权成立")🔰 攻防验证:委托 工信部电子四所 出具《功能不可替代性技术鉴定书》